Im

Prinzip funktioniert ein MFM Encoder genau umgekehrt wie der im

Kapitel 1.7 beschriebene MFM Decoder.

Ein MFM Encoder arbeitet

nach dem Prinzip von time-shifting und phase-shifting. Diese

Methode geht von der Übertragungsfrequenz aus und die MFM

Signale werden dann mit Hilfe der doppelten Frequenz gebildet.

Weitere Details über das MFM

Verfahren sind auf verschiedenen Seiten im Internet zu

erfahren.

Bei meinem RL02-Simulator

Projekt

habe ich mich einstweilen sehr gut in die

Hardwarebeschreibungssprache

Verilog

eingearbeitet

und mein fertiger

MFM-ENCODER

in

der Version V1.2 ist hier

mit

genauer Beschreibung ersichtlich.

Der

MFM Encoder bei meinem RL02-Simulator Projekt arbeitet mit einer

Übertragungsfrequenz von 4.1 MHz. Die nötigen 8.2 MHz

werden durch einen Teiler mit einer Eingangsfrequenz von 16.4 MHz

erzeugt. Die 16.4MHz sind historisch bedingt, da dieser MFM

Encoder auch bei meinem MAXII CPLD zum Einsatz kam, hier

allerdings kein PLL zur Verfügung stand, so dass die Frequenz

mit einem externen Oszillator erzeugt werden musste.

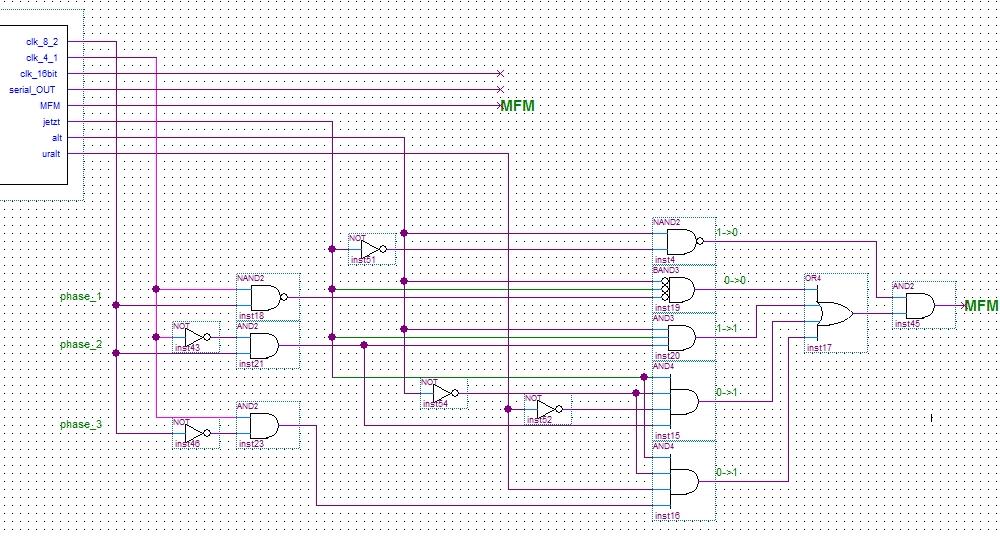

Im

folgenden Bild ist der eigentliche Encoder Teil als Schaltung

dargestellt, für Alle, die diese Darstellungsart einem

Verilog Programm-Code vorziehen.

Entwicklungsablauf:

Das

Entwickeln der einzelnen Komponenten durch Schaltungen und

Block-Diagramm bis runter auf Gatter Ebene gestaltete sich immer

mehr als problematisch und ineffizient. Diese Art der Entwicklung

habe ich aufgegeben, die Sprache Verilog gelernt und fast alle

Module neu entwickelt. Die einzelnen Schritte bei der Entwicklung

des MFM Encoder sind hier der Vollständigkeit halber auch

noch aufgezeigt:

A)

Erste Entwicklung mit Schaltung Block-Diagramm

B)

Zweite Entwicklung , mit Block-Diagramm und Verilog Modul.