MFM

Protokoll

, Übersicht

Unter

der Patent Nummer 4,376,958

wurde das MFM

(

Modified

Frequency

Modulation

) Verfahren vorgestellt. Weitere Details über das MFM

Verfahren sind auf verschiedenen Seiten im Internet zu

erfahren. Das MFM Verfahren wurde überwiegend bei Festplatten

und Diskettenlaufwerken eingesetzt mit der ST506 Schnittstelle.

DEC

RL02 MFM

DECODER

Die

Übertragungsrate bei den RL02 Laufwerken liegt bei 4.1

magabits/sec und

ist mit der 50MHz FPGA Clock somit schwer nachzubilden.( Bei

der ST506 Schnittstelle wären 5.0 MHz erforderlich und somit

leichter zu realisieren ).

Es gibt allerdings auch hier Lösungsmöglichkeiten ,

welche ich in folgenden 3 Kapiteln vorstellen will.

A) Analyse der MFM Signale und MFM DECODER ohne CLOCK RECOVERY

B) Realisierung eines MFM DECODER mit CLOCK and DATA RECOVERY ( CDR ), Messen der MFM Signale.

C) Fertiger MFM DECODER mit CLOCK and DATA RECOVERY( CDR )für DEC RL02 Laufwerke basierend auf Shift-Register mit Clock-Sync.

Hinweis:

Die

RL02 Cartridges wurden in der Factory Vor-Formatiert und das

Servo/Header Format war DEC intern streng geheim, um

sicherzustellen, dass die Kunden nur die relativ teuren Cartridges

von DEC kaufen mussten. Im Servo/Header Bereich der RL02

Cartridges tauchen ab und zu 0.125uS

oder 0.625uS ( 0.250uS, 0.325uS, 0.500uS is normal ) MFM Signale

auf und verursachen, dass mein MFM Decoder im Servo/Header Bereich

durcheinander kommt und nicht mehr synchronisiert ist. DEC hatte

dies damals mit einen ROM Code quasi ausgeglichen, welcher auf dem

RLV-11/12 Controller sitzt. Um diese leider undokumentierte

Gegebenheit im Kapitel C) zu umgehen, überspringe ich den

Servo/Header Teil und synchronisiere das MFM Timing neu in der

Data preample (PR2) Phase, welche aus 47 "0" und einen

marker "1" (Sync Bit) besteht. Bis die Servo/Header

Struktur nicht 100% klar ist, wird die MFM Clock bei Auftreten

eines noch unbekannten MFM Signal für 0.250uS ausgeschaltet.

Das 100%ige

Verstehen der Servo/Header Struktur ist allerdings unbedingte

Voraussetzung bei der Realisierung des noch nötigen MFM

ENCODER.

Dies ist ein offener Punkt und ich arbeite daran. Aus jetziger

Sicht wäre es viel einfacher gewesen , einen ST506

basierenden Disk Simulator zu entwickeln.

A)

Analyse der MFM Signale und MFM DECODER ohne CLOCK RECOVERY

Um

die MFM Signale zu analysieren benötigte ich ein

Test-Pattern, welches immer den gleichen Inhalt pro Sector zur

Verfügung stellt. Diese Test-Pattern habe ich mit einem RT-11

Basic Programm erzeugt

und war nun die ideale Ausgangsposition für eine genau

Analyse der MFM Signale. Mit einem Logic Analyser wurden die

MFM-Daten

gut

sichtbar. Der dazu nötige MFM Decoder war relativ einfach zu

realisieren weil das nötige Clock Signal beim Write Zyklus in

Form einer 4.1 Mhz Clock zur Verfügung steht. Dementsprechend

einfach sieht die Schaltung

aus.

Nun ist man zwar schon in der Lage, MFM Daten zu decodieren, aber diese Methode funktioniert nur, wenn ein Clock Signal zur Verfügung steht. Ein zweiter Nachteil dieser Methode ist auch , dass die Sector/Track Struktur und die Kontroll-Signale, wie SERVO und CRC später quasi manuell nachgebildet werden müssen. Also benötigen wir einen MFM DECODER mit CLOCK and DATA RECOVERY ( CDR), um alle Signale von der Disk zu erf assen.

B)

Realisierung eines MFM DECODER mit CLOCK

and DATA RECOVERY

(

CDR ), Messen der MFM Signale.

Um

die Clock aus den MFM Daten zu gewinnen benötigt man einen

PLL, welcher auch in den RLV-11/12 Disk Controllern zu finden ist.

Allerdings gibt es in der FPGA-Welt keinen PLL in der

herkömmlichen Form mit VCO. Anstelle des PLL wird nun der

DPLL

Algorithmus

benützt,

um das Clock Signal aus den MFM Daten zu gewinnen.

Bei dem RL02

Laufwerk sieht das dann wie folgt aus:

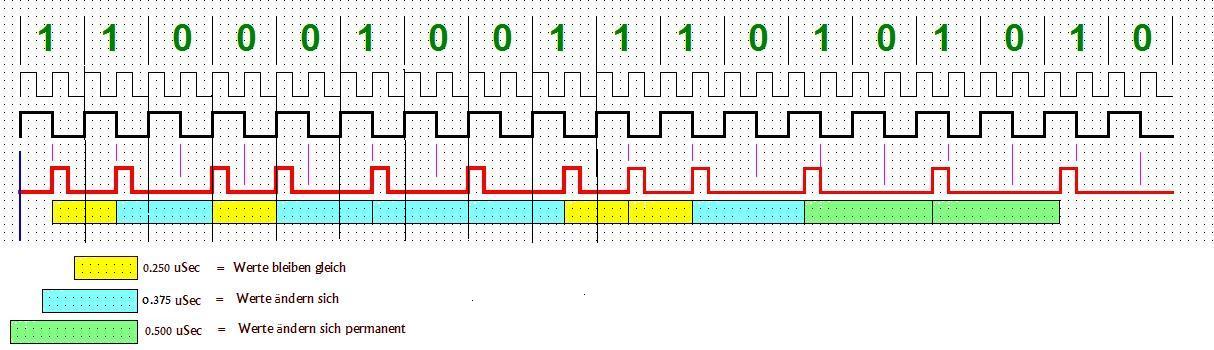

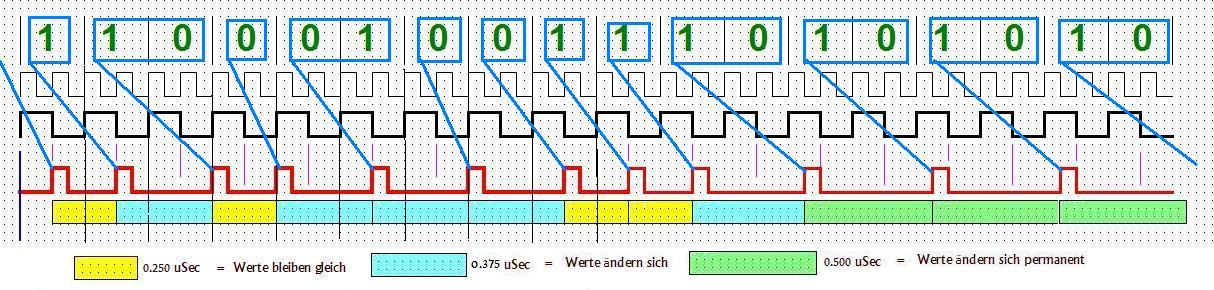

Die Daten werden mit

Phase-Shifting verändert. Es entstehen also verschiedene

Timing

Perioden in Abhängigkeit der sich veränderten Daten. Am

Beispiel des RL02 Laufwerks mit einer 4.1

Mhz Clock ergeben

sich folgende 3 unterschiedliche Perioden, welche dann wie folgt

aufgelöst werden können:

1) Kurze

Periode ,

0.250 uS ====>

Wert bleibt gleich 1111.... oder 0000.....

2) Lange

Periode ,

0.375 uS ====>

Wert ändert sich 000111 oder 100100

3) Sehr

lange Periode,

0.500uS ====>

Wert ändert sich kontinuierlich 01010101

Beispiel:

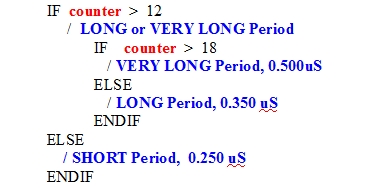

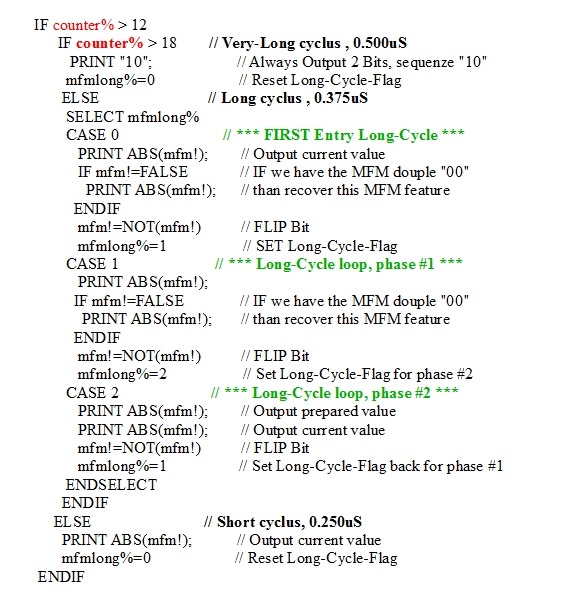

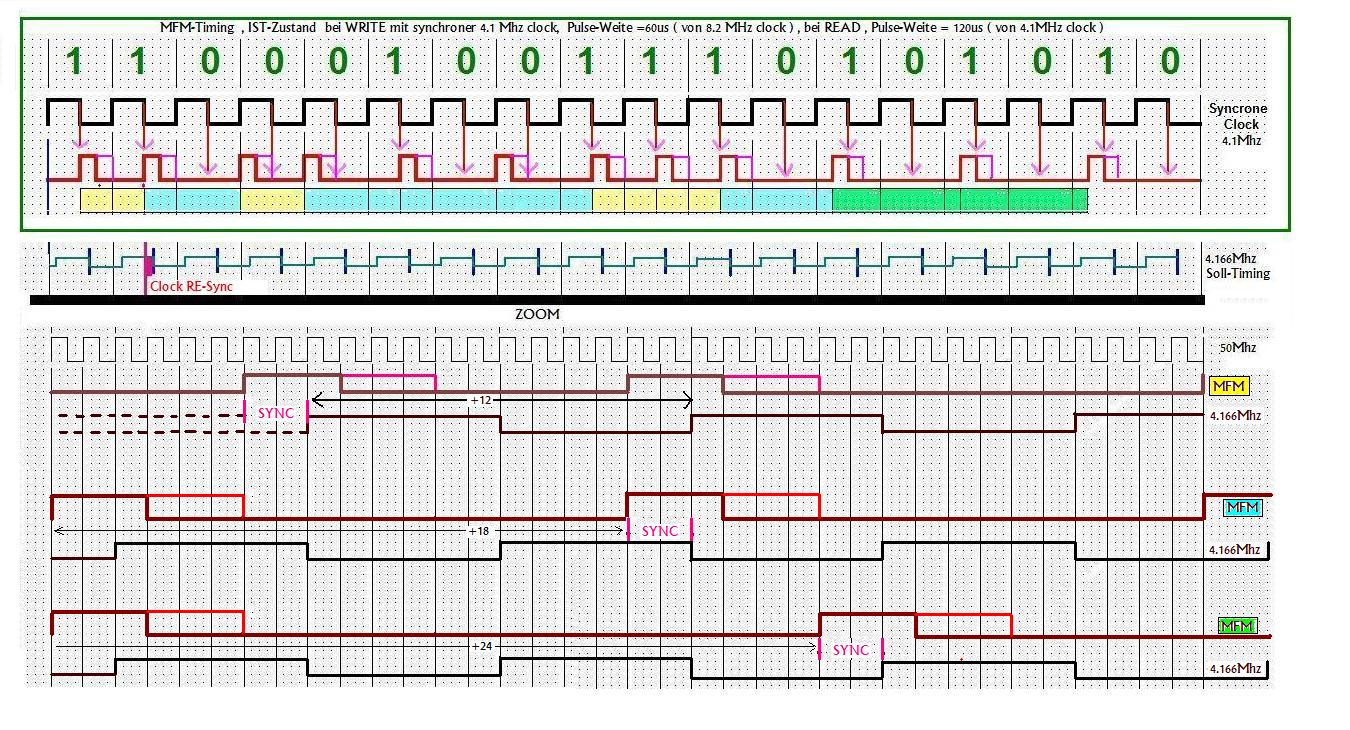

Nun müssen die Zeiten zwischen den MFM Signal Flanken mit einer wesentlich höheren Frequenz gemessen werden. Im Beispiel hier mit einer 50Mhz FPGA Clock. Die 3 verschiedenen MFM Signal-Perioden ergeben dann eine Zähler Auflösung für 12 = Kurze Periode, 18 = Lange Periode und 24 = Sehr Lange Periode.

Die Lösung zum Messen der MFM Flanken-Abstände sieht dann so aus:

Nun müssen noch die Daten aus der Abfolge der verschiedenen Perioden gewonnen werden. Wichtig ist, dass die Messung der Daten immer um eine Periode hinterher läuft. Der Algorithmus für den MFM DECODER sieht dann so aus:

Das ergibt dann folgenden Ablauf:

Im ersten Augenblick erscheint dieser Algorithmus eventuell etwas unklar und liegt wohl daran, dass beim MFM Verfahren bei einer doppelten „0“ die erste „0“ keine Clock hat, also quasi weg fällt und somit Platz spart. Weiterhin gilt, dass ein Long-Cycle immer eine Bit-Änderung zur Folge hat. Dabei gibt es eine besonders interessante Konstellation bei einer Bit-Sequenz “100100100100...“ , welche einen Long-Cycle Loop zur Folge hat.

Implementierung: Das

komplette MFM-Decoder

Programm habe

ich in GFA-Basic/Pascal entwickelt, weil es für mich nichts

Schnelleres gibt beim Entwicklung und Testen eines Algorithmus.

Status:

Diese

effektive und elegante Lösung ist noch nicht abgeschlossen,

denn ich will den Algorithmus mit Verilog

implementieren

und dazu habe ich derzeit noch zu wenig Erfahrung. Wenn es fertig

ist, werde ich den Code veröffentlichen. Derzeit kann ich die

MFM Zyklen mit einen 50Mhz FPGA Zähler erfassen, die Daten

zur ARM oder NIOSII CPU senden und dort decodieren lassen. Aber

auch hier laufe ich noch in das bereits beschriebene Problem im

Servo/Header Bereich der MFM Daten ( siehe Hinweis in Übersicht

).

C) Fertiger MFM DECODER mit CLOCK and DATA RECOVERY( CDR )für DEC RL02 Laufwerke basierend auf Shift-Register mit Clock-Sync.

Dieser lauffähige MFM Decoder beruht auf einer anderen Lösungsmöglichkeit. Leider kann man mit der 50Mhz FPGA Clock nicht die erforderliche 4.1Mhz Clock Phasen-Synchron zu den MFM Signalen rekonstruieren. Eine annähernde Frequenz von 4.1666 Mhz bekommt man allerdings mit einen 12:1 Teiler bei der 50Mhz standard FPGA-Clock als Eingans-Signal. Es gilt nun, diesen 12:1 Teiler richtig zu synchronisieren, was allerdings nicht einfach war. Folgendes Bild veranschaulicht die Problematik :

Der 12:1 Teiler muss also in Abhängigkeit der 3 möglichen MFM Zyklen und dem aktuellen BIT-Status entweder mit einem CLEAR oder einen PRESET immer neu synchronisiert werden sonst läuft der etwas zu schnelle 4.1666 Mhz Clock raus.Mein Design beruht auf einer Schaltung, bestehend aus dem MFM-DECODER und einen Serial nach 16 Bit parallel Konverter um die Daten bequem in einen FIFO , Dual-Port RAM oder ARM CPU weiter verarbeiten zu können. Mit folgenden Komponenten kann man einen Sektor und/oder Track auslesen:

Version

1.0

-

Grundschaltung

zum

Auslesen eines Sectors und/oder Track.

- Das Herzstück ,

der MFM-DECODER

-

ein Serial-16Bit

Konverter

und

folgende Zusatz-Komponenten:

- 12:1

Divider

-

Zyklus-Starter

-

2 different 8-16-128 Bit Counters, Typ_A

and

Typ_B

-

Delay

logic

Version

2.0

Bisher war es nicht möglich die HEADER Daten aus

den Disk-Servo Informationen zu lesen. Da die Header Daten sehr

wichtig sind für die Projekt Fertigstellung , habe ich den

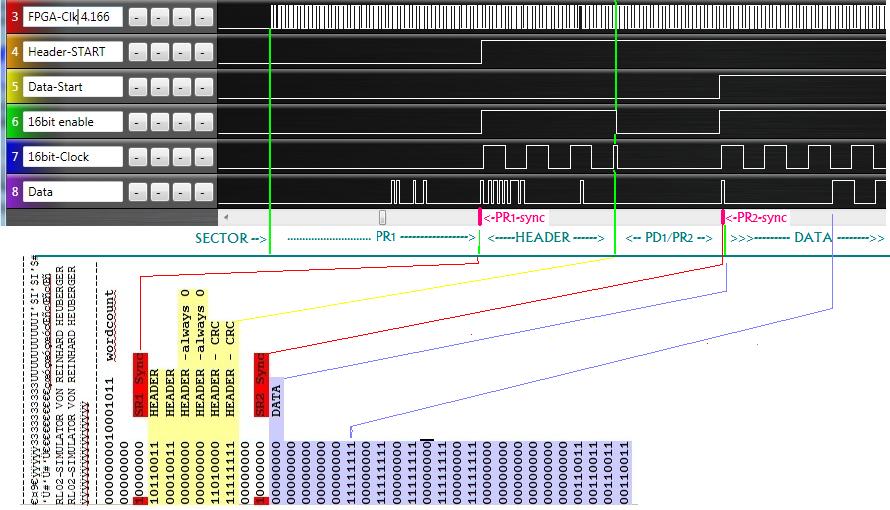

MFM-Decoder dementsprechend abgeändert. Folgendes Bild

veranschaulicht die Funktionsweise:

Weitere Informationen dazu auch im Vintage-Computer-Forum. Der überarbeitete MFM-Decoder, Version 2.0 hat nun einen 16Bit parallelen und seriellen Ausgang mit den dazugehörigen STROBE Signal. Mit folgenden Komponenten kann man den Header und die Daten von einen Sector/Track auslesen:

-

Grundschaltung

zum

Auslesen eines Sectors und/oder Track.

- Das Herzstück ,

der MFM-DECODER-V2

Folgende

Zusatz-Komponenten:

- 12:1

Divider

-

Zyklus-Starter

-

16Bit_synchron_counter

-

8_16_64_128_Counter_C

-

Delay

logic

Alle Dateien sind im JPG-Format. Für Altera/Quartus Anwender kann ich gerne den gesamten Ordner mit den ARM Programmen im ZIP Format zur Verfügung stellen. Bei Bedarf bitte Kontakt per E-Mail.