### Development of the RK05 emulator

www.pdp11gy.com

## **Prototyp Interface board**

Project start: January 2023

Also based on De10-Nano FPGA Board: http://pdp11gy.com/rk05\_E.html Reference projects: RL01/RL02 emulator: http://pdp11gy.com/rlstatusE.html

MFM-Disk emulator: <a href="http://pdp11gy.com/sddoneE.html">http://pdp11gy.com/sddoneE.html</a>

Open Source: <a href="https://github.com/pdp11gy/RK05-Disk-Emulator">https://github.com/pdp11gy/RK05-Disk-Emulator</a>

# Emulates up to 4 RK05 drives simultaneously Supports mixed environment of emulated + real RK drives

**Emulator Mode** This mode supports a combination of real and emulated RK05 disk drives. Thus, it is possible to copy the data from a real disk drive into the emulated environment. However, there is still a computer system, e.g. a PDP-8 required. The interface is working in **Slave Mode** with the program **rkemulator** Note: The Clone/Read mode = Master Mode is not implemented yet.

Data format (PDP-8 mode): The DEC RK05 disk drive did have a capacity of ~2.5 MB The emulater is using the .dec format which contains all the sector information . Another disk format is the disk image structure .dsk which is used for CPU emulators like SIMH. At write operation, the .dec file and the .dsk file will be written. At read operation, first try is to read the .dec file. If it does not exist, the .dsk file will be read.

RK05: .dsk file 3245728 byte .dec file = 3338752 byte

Assuming the 4 slide switches on the DE10-Nano board are in off position, the emulator will generate 4 emty .dsk and .dec file : rk05-0 to rk05-3

Open:

PDP-11 mode not implemented yet (16 sector /track)

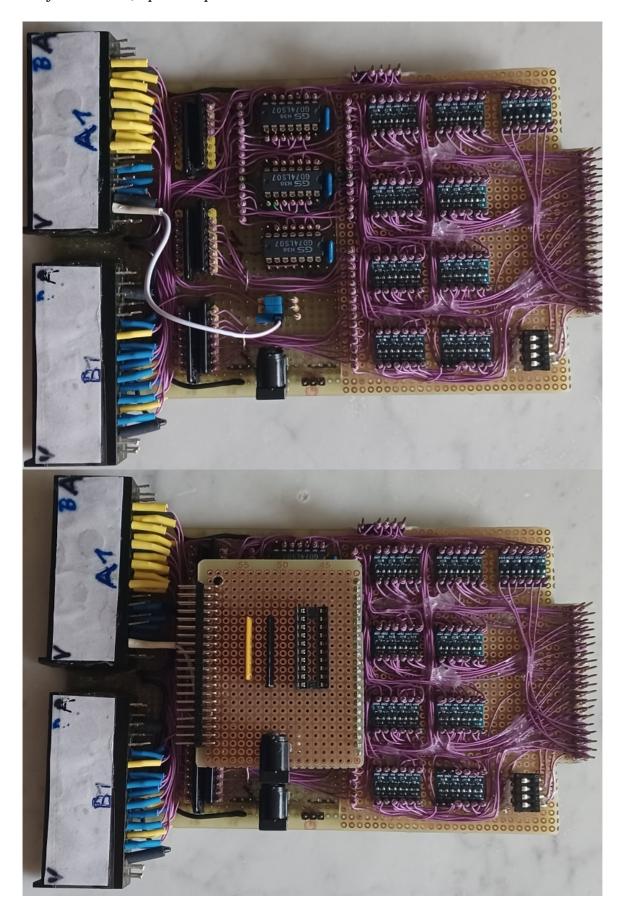

PCB board not available yet, only one prototyp interface board

Test/verify environment not available, Hopefully starting June this year

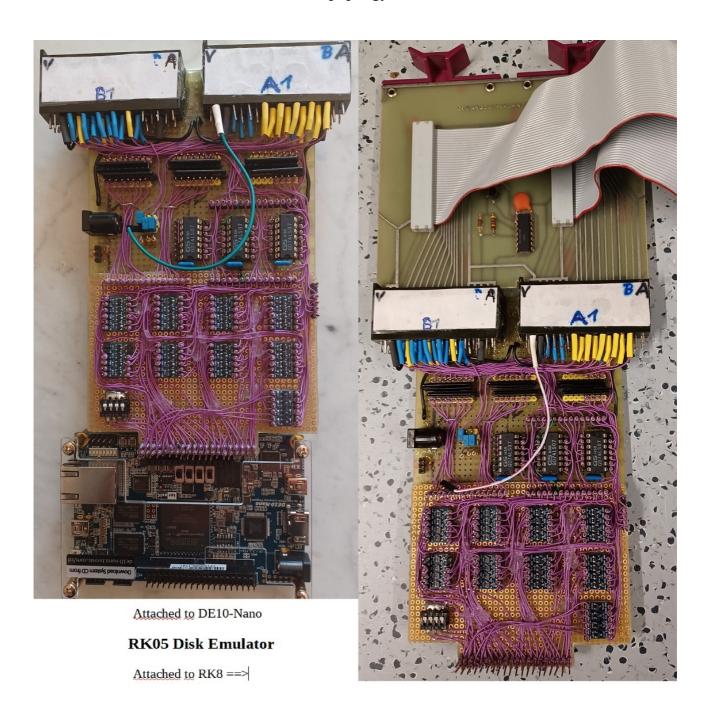

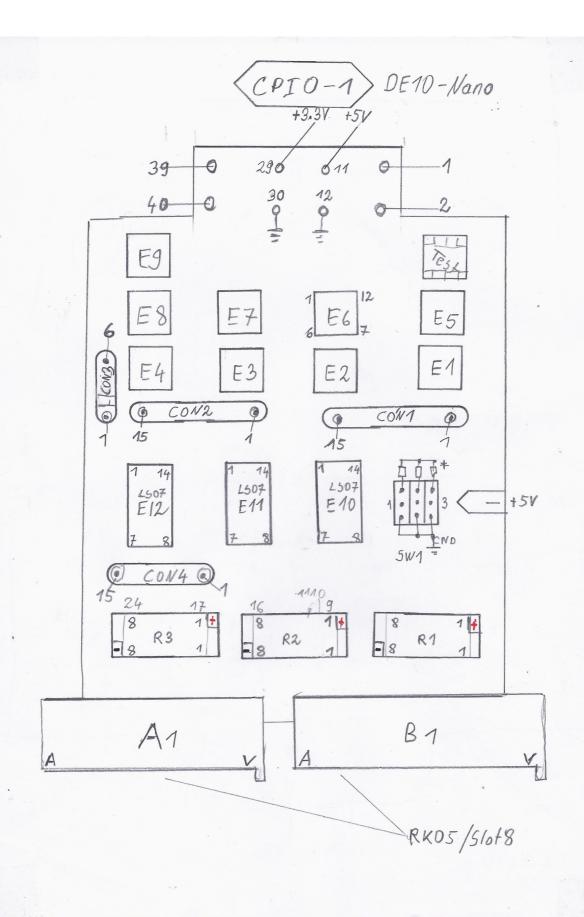

#### (Prototype) Hardware

The DE10-Nano board has 2 CPIO connectors available with 40 pins each, but 4 are always occupied. Thus 36 pins are freely available. However, the RK05 I/O bus consists of 38 signals, 20 for input and 18 for output. Result: 2 signals are too many. I solved this problem by not using unnecessary signals and permanently setting them to high or low. These signals are ADDRESS INVALID and SEEK INCOMPLETE and HIGH DENSITY( output ). One PIN is thus left and it will be used to select PDP-8 or PDP-11 mode.

A full, **ready for use** configured <u>SD-card-image</u> for the DE10-Nano Board is also available. Download the image from my homepage and copy it to the SD card with Win32DiskImager, for example. Login: root, PW: pdp11. The associated directory is rk

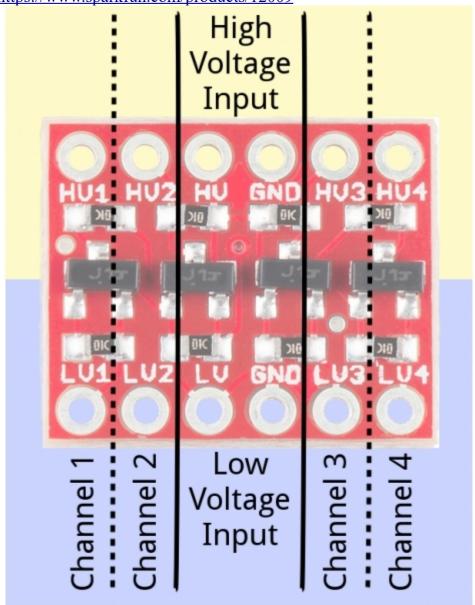

Some hints: It is obvious that a RX01/RX02 emulator can be developed with relatively little effort. There are already such RX-floppy emulators, but not together with an RK05, RL01/02 and MFM-disk emulator. My plan is to develop a PCB board with level shifters for all 36 signals on the DE10-Nano board. Small interfaces can then be plugged onto this board for RL01/R02, MFM, RK05 and RX01/RX02 emulated disk drives.

| × 54/11   | HIGH-NEWSILY EHM                             | PIN_AE17 | 1540 2 GPIO_1[35]         | GPIO_1[34] 5 3914 @ 640 2 GPIO_1[35]                                | E4/8 RESTORE PIN_AE19           |

|-----------|----------------------------------------------|----------|---------------------------|---------------------------------------------------------------------|---------------------------------|

| 27/43     | AC-DC                                        | PIN_AE20 | 1438 / GPIO_1[33]         | GPIO_1[32] 6 37 13 @ 1438 1 GPIO_1[33]                              | E4/7 WRITE_GATE PIN_AG15        |

|           | PIN_AFZO THDEX-PULSE                         | PIN_AF20 | 1336 7 GPIO_1[31]         | GPIO_1[30] 1 3512 ( 1336 1 GPIO_1[31]                               | E8 M2WRITE_DATA_AND_COMMIN_AF18 |

| E3/11     | SECTOR-PULSE                                 | PIN_AH18 | 234 2 GPIO_1[29]          | GPIO_1[28] 2, 3311 (234 2 GPIO_1[29]                                | Same                            |

| 35-JE3/8  | PIN_AH19 SECTOR_ADURESS-JE3/8                | PIN_AH19 | 1132 5 GPIO_1[27]         | GPIO_1[26] 6 31 10 0 0 1132 5 GPIO_1[27]                            | E8/7HEAD_SELECTPIN_AG19         |

| 2 7       | 7                                            |          | 30 GND                    | 3.3V 29                                                             | K8/8                            |

| 5-413/7   | PIN_AF21 SECTOR_ADDRESS-4E3/7                | PIN_AF21 | 1028 8 GPIO_1[25]         | GPIO_1[24] 5 27 9 028 6 GPIO_1[25]                                  | 5TROBE PIN_AG20                 |

| 5-1/E2/8  | SECTOR_ADDRES                                | PIN_AE22 | 926 5 GPIO_1[23]          | GP10_1[22] 6 25 8 926 5 GP10_1[23] PIN_AEZZ SECTOR_AODRESS - 1 F2/8 | ET 17 CYLINDER - A7 PIN_AF22    |

| 15-0 EV/7 | PIN_AA20 SECTOR_ADDRESS-0/EX/7               | PIN_AA20 | 824 6 GPIO_1[21]          | GPIO_1[20] 5 23 ₹ 824 6 GPIO_1[21]                                  | F7/2 CYLINDER_A6 PIN_AH23       |

| 17/27     | READ-CLOCK                                   | PIN_AG21 | 722 2 GPIO_1[19]          | GPIO_1[18] 2 21 6 722 2 GPIO_1[19]                                  | E7/11 CYLINDER -A5. PIN_AH21    |

| T2/2      | PIN_AH22 READ_DAIA F2/2                      | PIN_AH22 | 620 4 GPIO_1[17]          | GPIO_1[16] /1 19:5 620 / GPIO_1[17]                                 | E7/12 CYLINDER_A4 PIN_AG24      |

| M 6/8     | PIN_AF23 WRITE-CHECK                         | PIN_AF23 | \$18 5 GPIO_1[15]         | GPIO_1[14] 2 17 + S 18 5 GPIO_1[15]                                 | EG/11 CYLINDER -A3 PIN_AG23     |

| SIAIUE6/F | WRITE PROLECT                                | PIN AF25 | 416.6 GPIO_1[13]          | GPIO_1[12] / 15 3 416 6 GPIO_1[13]                                  | EG /12 CYLINDER_A2 PIN_AH24     |

| PLETE(Y.  | [14] GPIO_1[11] PIN_AHZE SEEK_TUCOMPLETE(1). | PIN_AH2€ | (14) GPIO_1[11]           | GPIO_1[10] 2 13 2                                                   | · ES / AD CYLINDER_AT PIN_AG25  |

| )         |                                              |          | 12—GND                    | 5V 11 0                                                             |                                 |

| 4LIDE     | ADDRESS - TWVALIDE                           | PIN_AH27 | (10) GPIO_1[9]            | GPIO_1[8] 19 1                                                      | VES 112 CYLINDER_AD PIN_AG26    |

| + Child   | ADDRESS - 4 CO                               | PWW_AF27 | 38 6 GPIO_1[7]            | GPIO_1[6] 7-                                                        | SELECT-3 PIN_AE25               |

| F1/8      | R-W-S-READY F1/8                             | PM AF28  | 5- 0 26 5 GPIO_1[5]       | GPIO_1[4] 5-                                                        | SELECT-2 PIN_AG28               |

| EN/M      | FILE_READY                                   | PIN_AD26 | 3 - 0 14 2 GPIO_1[3]      | GPIO_1[2] 3-                                                        | SELECT_7 PIN_AA15               |

| E1/12     | READ_GATE                                    | PIN_AC24 | 1 - 0 0/52 · 1 GPIO_1[1]. | GPIO_1[0] 1 →                                                       | SELECT_O PIN_Y15                |

| 1         |                                              |          | (197)                     | GPIO 1 (JP7)                                                        | DE10-Nano                       |

|           |                                              |          |                           |                                                                     |                                 |

## **INPUT Signals = TO FPGA** $\leftarrow$ **Host**

| Signal NAME          | FPGA/PIN | CON/PIN | R-Net | RK05/Slot8 |

|----------------------|----------|---------|-------|------------|

| SELECT 0             | Y15/1    | CON3/6  | R3-5  | A08-J2     |

| SELECT 1             | AA15/3   | CON3/5  | R3-6  | A08-K2     |

| SELECT 2             | AG28/5   | CON3/4  | R3-7  | A08-L2     |

| SELECT 3             | AE25/7   | CON3/3  | R3-8  | A08-M2     |

| CYLINDER ADDRESS 0   | AG26/9   | CON1/1  | R1-1  | A08-K1     |

| CYLINDER ADDRESS 1   | AG25/13  | CON1/2  | R1-2  | A08-D1     |

| CYLINDER ADDRESS 2   | AH24/15  | CON1/3  | R1-3  | A08-L1     |

| CYLINDER ADDRESS 3   | AH23/17  | CON1/4  | R1-4  | A08-C1     |

| CYLINDER ADDRESS 4   | AG24/19  | CON1/5  | R1-5  | A08-F1     |

| CYLINDER ADDRESS 5   | AH21/21  | CON1/6  | R1-6  | A08-J1     |

| CYLINDER ADDRESS 6   | AH23/23  | CON1/7  | R1-7  | A08-E1     |

| CYLINDER ADDRESS 7   | AF22/25  | CON1/8  | R1-8  | A08-H1     |

| STROBE               | AG20/27  | CON1/9  | R2-1  | B08-H1     |

| HEAD SELECT          | AG19/31  | CON1/10 | R2-2  | B08-M2     |

| WRITE PROTECT SET    | AG18/33  | CON1/11 | R2-3  | B08-R2     |

| WRITE DATA AND CLOCK | AF18/35  | CON1/12 | R2-4  | B08-F2     |

| WRITE GATE           | AG15/37  | CON1/13 | R2-5  | B08-L2     |

| RESTORE              | AE19/39  | CON1/14 | R2-6  | B08-M1     |

| READ GATE            | AC24/2   | CON1/15 | R2-7  | B08-R1     |

|                      |          |         |       |            |

Termination, all input signals @ CON3 and CON1

!50 Ohm to +5 V 330 Ohm to GRND

## **OUTPUT Signals FROM FPGA** $\rightarrow$ **Host**

| Signal NAME          | FPGA/PIN | CON/PIN | E10-E11   | RK05/Slot8 |

|----------------------|----------|---------|-----------|------------|

| FILE READY           | AD26/4   | CON2/1  | E10-5/6   | B08-N1     |

| R/W/S READY          | AF28/6   | CON2/2  | E10-3/4   | A08-H2     |

| ADDRESS ACCEPTED     | AF27/8   | CON2/3  | E10-1/2   | A08-R2     |

| (ADDRESS INVALID)    | AH27/10  | %       | %         | *(A08-T2)  |

| (SEEK INCOMPLETE)    | AH26/14  | %       | %         | *(A08-S2)  |

| WRITE PROTECT STATUS | AF25/16  | CON2/4  | E11-13/14 | B08-P1     |

| WRITE CHECK          | AF23/18  | CON2/5  | E11-11/10 | B08-K1     |

| READ DATA            | AH22/20  | CON2/6  | R11-9/8   | B08-S2     |

| READ_CLOCK           | AG21/22  | CON2/7  | E11-5/6   | B08-S1     |

| SECTOR ADDRESS 0     | AA20/24  | CON2/8  | E11-3/4   | B08-L1     |

| SECTOR ADDRESS 1     | AE22/26  | CON2/9  | E11-1/2   | A08-P2     |

| SECTOR ADDRESS 2     | AF21/28  | CON2/10 | E12-13/12 | A08-K2     |

| SECTOR ADDRESS 3     | AH19/32  | CON2/11 | E12-11/10 | A08-J1     |

| SECTOR PULSE         | AH18/34  | CON2/12 | E12-9/8   | A08-N2     |

| INDEX PULSE          | AF20/36  | CON2/13 | E12-5/6   | A08-M1     |

| DC-LOW               | AE20/38  | CON2/14 | E12-3/4   | A08-F2     |

| AC-LOW               | AE17/40  | CON2/15 | E12-1/2   | A08F1      |

|                      |          |         |           |            |

### Not connected FPGA PIN's:

| *ADDRESS INVALID - AH27/10 dropped → SW1/1 | A08-T2   | HIGH |

|--------------------------------------------|----------|------|

| *SEEK INCOMPLETE – AH26/14 dropped → SW1/2 | 2 A08-R2 | HIGH |

| HIGH DENSITY $\rightarrow$ SW1/3           | B08-P2   | LOW  |

https://www.sparkfun.com/products/12009

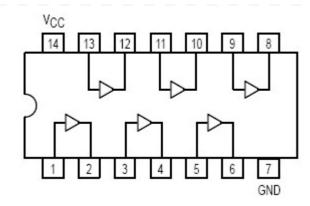

SN74LS07 Hex Buffers and Drivers With Open-Collector

It's just an idea, open but possible: attached RX01/RX02 interface.